**Gokaraju Rangaraju

Institute of Engineering and Technology

(Autonomous Institution under JNTU Hyderabad)**

**Principles of Analog Electronics

Lab Record**

***Name:***

***Roll No:***

***Course: B.Tech. II Yr I Semester***

***Branch: EEE***

# **CERTIFICATE**

***This is to certify that a bonafide record of practical work done***

***by Mr. /Ms. \_\_\_\_\_***

***Reg. No. \_\_\_\_\_ in the PRINCIPLES OF ANALOG***

***ELECTRONICS LABORATORY in the II Year I Semester during***

***20\_\_\_\_ - 20\_\_\_\_.***

Internal Examiner

Signature

External Examiner

Signature

# **PRINCIPLES OF ANALOG ELECTRONICS LAB**

## **II Year I Semester**

### **Course Objectives:**

After completion of this course, Students must be able to

1. Classify the types of active components.

2. Describe the operations of Diode and BJT

3. Analyze different Configuration types of Operational Amplifier.

4. Implement the mathematical operation on signals.

5. Make conversant with Oscillator principle

### **Course Outcomes:**

After completion of this course, Students will be able to

1. Recall types of active components.

2. Illustrate the characteristics of Diode and BJT

3. Design Operational Amplifiers as inverting and non-inverting amplifier

4. Apply mathematical operation on signals using Operational Amplifier

5. Design Oscillator circuit

## CONTENTS

| <b>S. No</b> | <b>Topic</b>                              | <b>Page No</b> |

|--------------|-------------------------------------------|----------------|

| i.           | Introduction to Analog Discovery Kit      | 1              |

| ii.          | Steps to run WAVEFORMS Software           | 3              |

| 1            | Diode Characteristics                     | 6              |

| 2            | Half Wave Rectifier Using Diode           | 10             |

| 3            | Clipping Circuits                         | 13             |

| 4            | Clamping Circuits                         | 22             |

| 5            | BJT Static Characteristics                | 26             |

| 6            | JFET Drain Characteristics                | 32             |

| 7            | Inverting Amplifier                       | 34             |

| 8            | Exercise on Non-Inverting Amplifier       | 38             |

| 9            | Subtractor Circuit/Differential Amplifier | 44             |

| 10           | Integrator Circuit                        | 47             |

| 11           | Differentiator Circuit                    | 51             |

| 12           | Design of RC Phase shift Oscillator       | 54             |

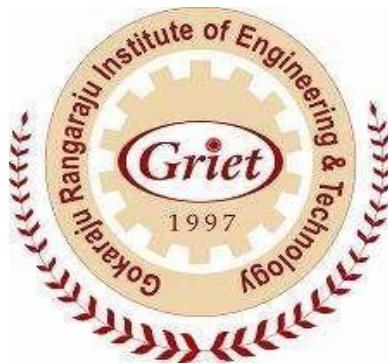

# INTRODUCTION TO ANALOG DISCOVERY KIT

## Overview

The Digilent Analog Discovery, developed in conjunction with Analog Devices Inc., is a multi-function instrument that can measure, record and generate analog and digital signals.

**Figure:** Analog Discovery used in a circuit design experiment

The small, portable and low-cost Analog Discovery (above Figure) was created so that engineering students could work with analog and digital circuits anytime, anywhere - right from their PC. The Analog Discovery's analog and digital inputs and outputs connect to a circuit using simple wire probes. Inputs and outputs are controlled using the free PC- based Waveforms software that can configure the Discovery to work as any one of several traditional instruments. Instruments include:

- Two channel oscilloscope ( $1M\Omega$ ,  $\pm 25V$ , differential, 14 bit, 100Msample/sec, 5MHz bandwidth);

- Two channel arbitrary function generator ( $22\Omega$ ,  $\pm 5V$ , 14 bit, 100Msample/sec, 5MHz bandwidth);

- Stereo audio amplifier to drive external headphones or speakers with replicated AWG signals;

- 16-channel digital logic analyzer (3.3V CMOS, 100Msample/sec)\*;

- 16-channel pattern generator (3.3V CMOS, 100Msample/sec)\*;

- 16-channel virtual digital I/O including buttons, switches and LEDs –good for logic trainer applications\*;

- Two input/output digital trigger signals for linking multiple instruments (3.3V CMOS);

- Two power supplies (+5V at 50mA, -5V at 50mA).

- Single channel voltmeter (AC, DC,  $\pm 25V$ );

- Network analyzer – Bode, Nyquist, Nichols transfer diagrams of a circuit. Range: 1Hz to 10MHz;

- Spectrum Analyzer - power spectrum and spectral measurements (noise floor, SFDR, SNR, THD, etc.);

- Digital Bus Analyzers (SPI, I2C, UART, Parallel);

The Analog Discovery was designed for students in typical university-based circuits and electronics classes. Its features and specifications, including operating from USB power, a small and portable form factor, and the ability to be used by students in a variety of environments at low cost, are based directly on inputs from many professors at many universities. Meeting all the requirements proved challenging, and resulted in some new and innovative circuits. This document is a reference for the Analog Discovery's electrical functions and operations. This reference also provides a description of the hardware's features and limitations. It is not intended to provide enough information to enable complete duplication of the Analog Discovery, or to allow users to design custom configurations for programmable parts in the design.

The pin-out terminals of Analog Discovery Kit (AD Kit) is shown below

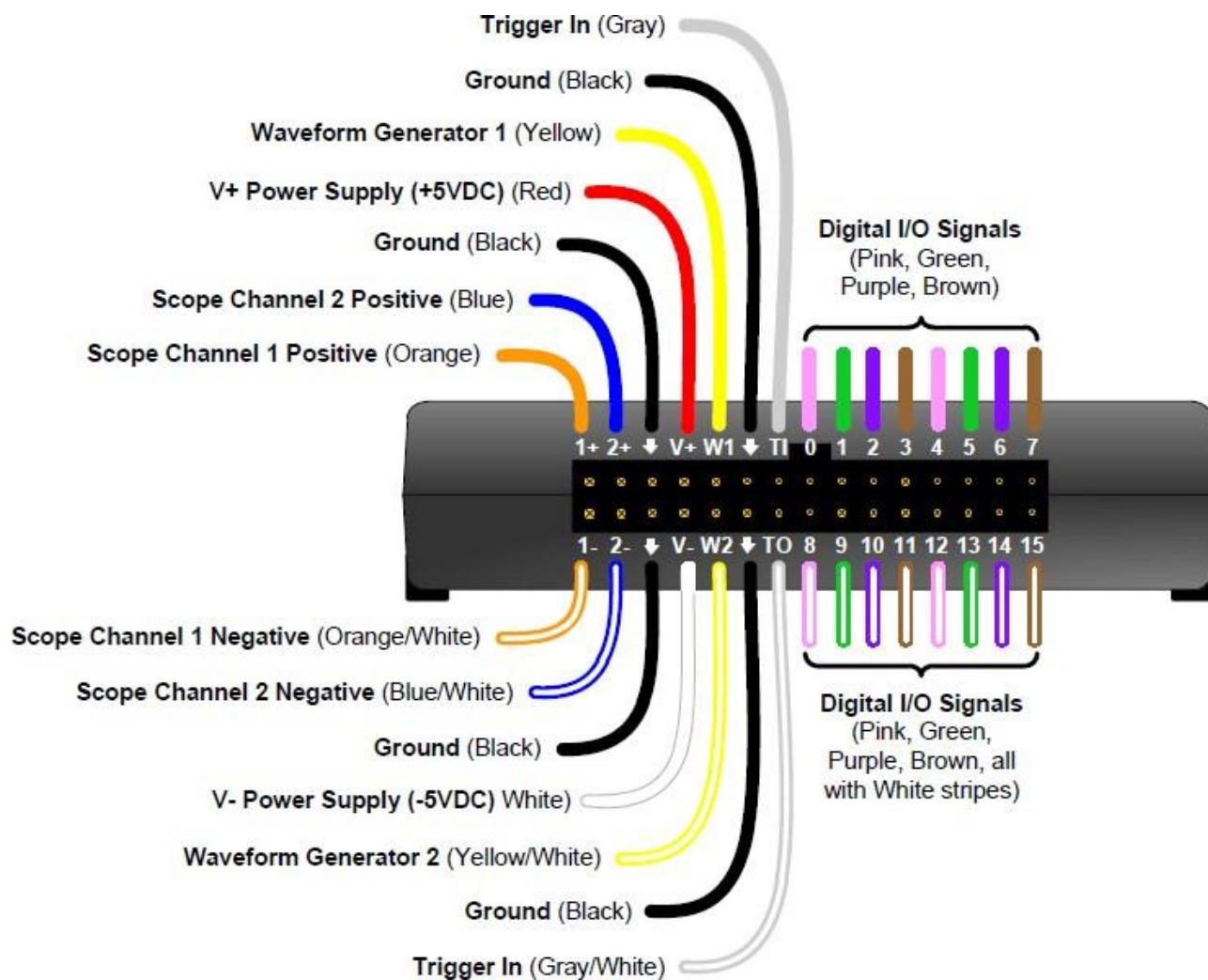

# STEPS TO RUN WAVEFORM SOFTWARE

**Step1:** Open the “Waveform” software from the start menu of the windows desktop

**Figure: Showing the selection of Waveform software from the start menu**

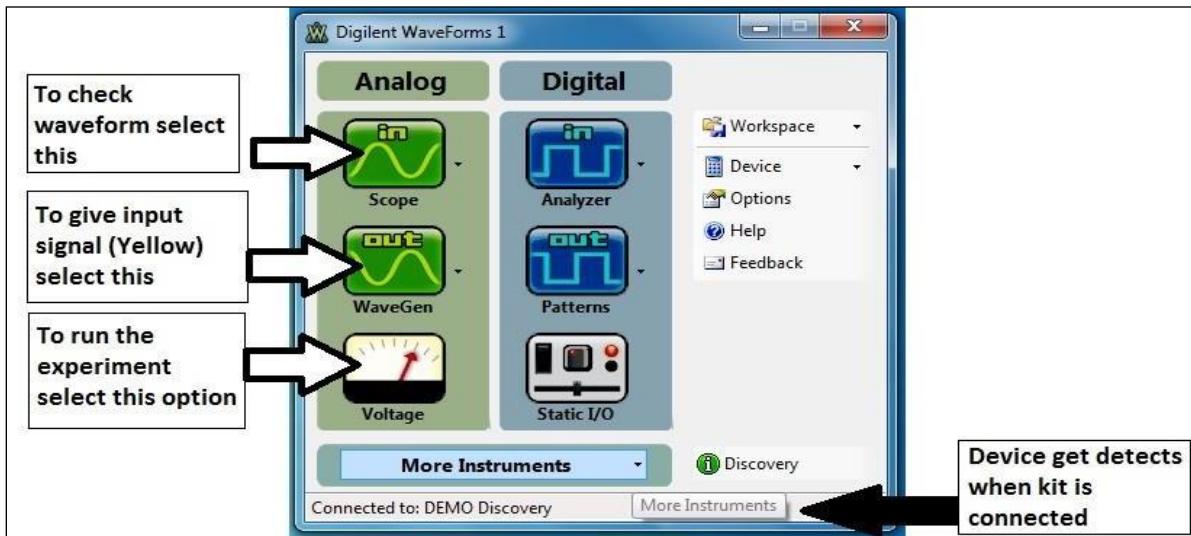

**Step2:** Each block representation of Waveform software

“in” -To check waveforms at the output terminals of the hardware connections done on Bread board “in” is selected

“out”- To give different input signals to the circuit done on the Bread board “out” is selected

“voltage”-This option is selected to apply +Vcc and –Vcc to the circuit connections done on Bread board

Figure: showing the Window of Waveform software

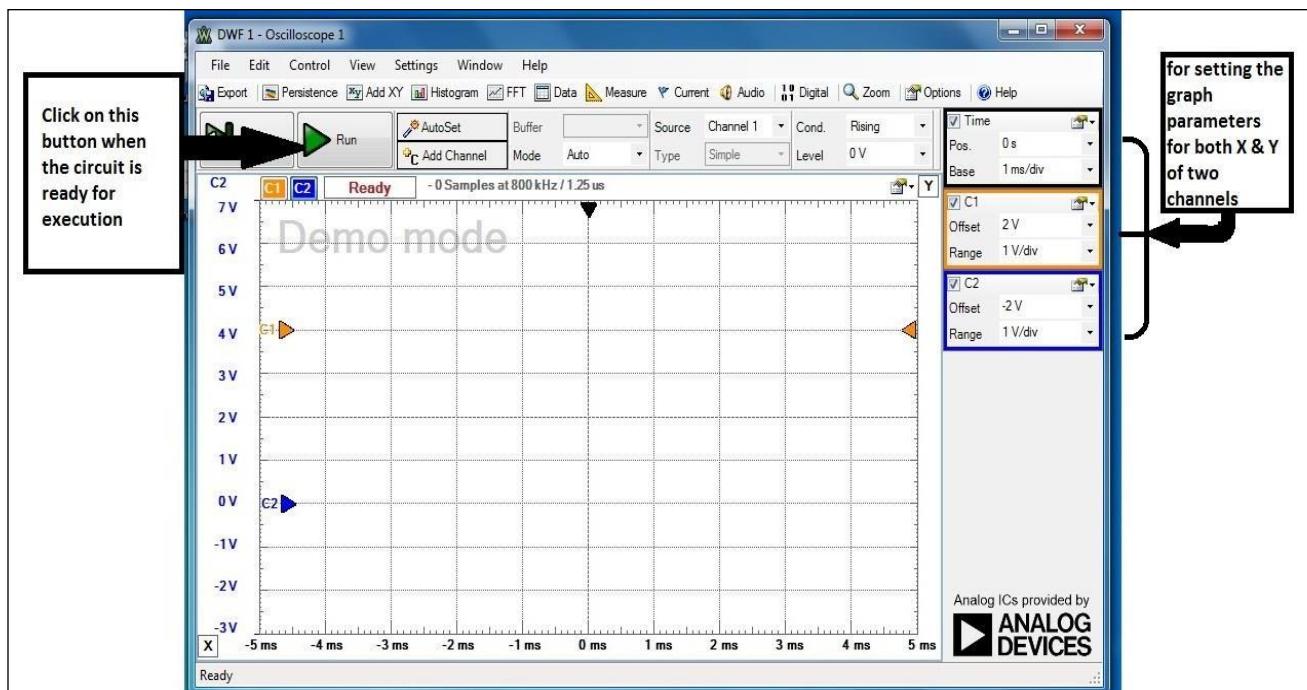

**Step 3:** The window shown below is obtained when “in” is selected from the “Waveform” software. Two waveforms can be seen at one time (one is “orange” and the other is “Blue”). The right side window shows the settings of different waveforms who’s Y and X axis can be set. After selecting the required options, click the “Run” button on Top left side of the Window to see the obtained output of the circuit connected on the Bread board.

Figure: Shows the “in” window of “Waveform” software

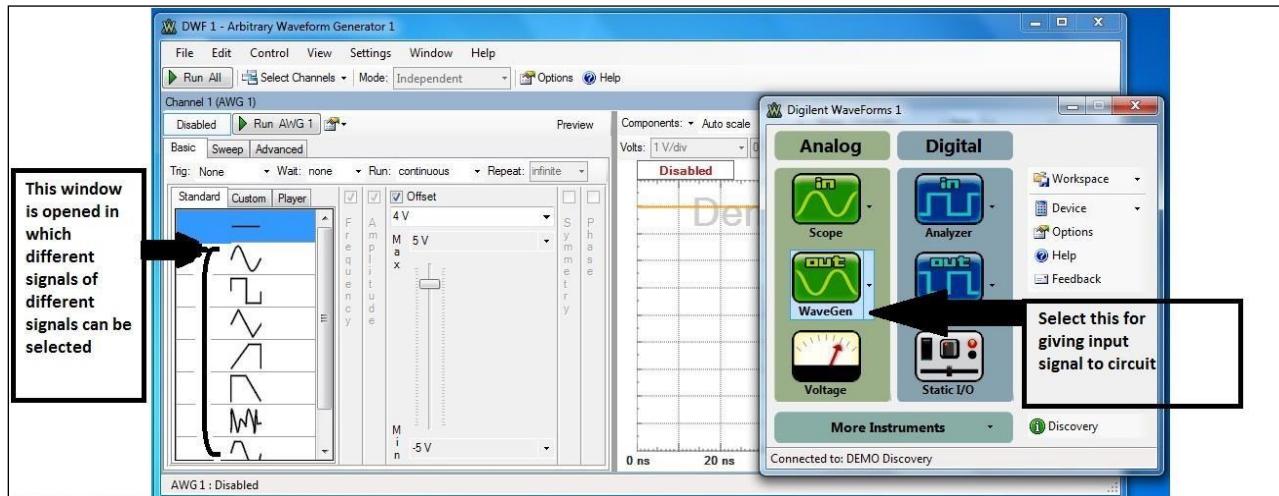

**Step4:** “Out” tab of Waveform software is used for selecting the types of waveforms like-sinusoidal, square, triangular, trapezoidal, random signal of different frequencies from this window. The signal

selected from this window is given as input signal to the circuit connected on the Bread board. After making the required settings click on the “Run AWG1” option from the window.

Figure: The “Out” window of Waveform in which different waveforms can be given as input

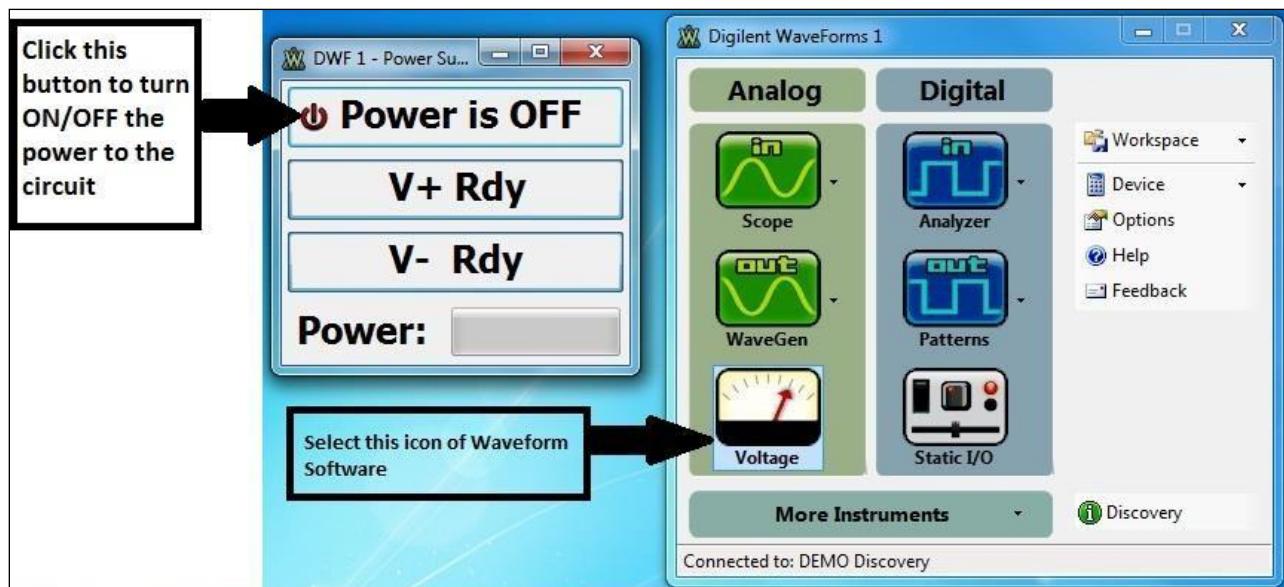

**Step5:** “Voltage” is selected for giving the input voltage of either +Vcc (Constant +5V) or –Vcc (Constant -5V) or both. When the “Power is ON/OFF” is selected the respective voltages are applied to the circuit connected.

Figure: The “Voltage” window of Waveform helps to run the ADE kit

# EXPERIMENT-1

## DIODE CHARACTERISTICS

**AIM:** To study and verify the PN Junction Diode characteristics

### APPARATUS:

Resistors (1 KΩ) – 1

Diode (1N4007) – 1

Analog Discovery Kit / ESIM Software / EC Studio Software

Connecting wires

Bread board

### THEORY:

- **Biassing of PN junction Diode:**

**Forward bias operation:** The P-N junction supports uni-directional current flow. If +ve terminal of the input supply is connected to p-side and –ve terminal is connected to n-side, then diode is said to be forward biased condition. In this condition the height of the potential barrier at the junction is lowered by an amount equal to given forward biasing voltage. Both the holes from p-side and electrons from n-side cross the junction simultaneously thereby decreasing the depleted region. This constitutes a forward current (majority carrier movement – diffusion current). Assuming current flowing through the diode to be very large, the diode can be approximated as short-circuited switch. Diode offers a very small resistance called **Forward resistance** (few ohms).

**Reverse bias operation** If negative terminal of the input supply is connected to p-side and –ve terminal is connected to n-side then the diode is said to be reverse biased. In this condition an amount equal to reverse biasing voltage increases the height of the potential barrier at the junction. Both the holes on P-side and electrons on N-side tend to move away from the junction thereby increasing the depleted region. However, the process cannot continue indefinitely, thus a small current called reverse saturation current continues to flow in the diode. This current is negligible; the diode can be approximated as an open circuited switch it offers a very high resistance called **Reverse resistance** (few Kiloohms)

**Static Resistance:** The opposition offered by a diode to the direct current flowing forward bias condition is known as its DC forward resistance or Static Resistance. It is measured by taking the ratio of DC voltage across the diode to the DC current flowing through it at an operating point.

**Dynamic Resistance:** The opposition offered by a diode to the changing current flow I forward bias condition is known as its AC Forward Resistance. It is measured by a ratio of change in voltage across the diode to the resulting change in current through it for an operating point P.

**Average Resistance:** Same as dynamic resistance but measured between extremities. Diode current equation

The volt-ampere characteristics of a diode explained by the following equations:

$$I = I_0(e^{\frac{V}{V_T}} - 1)$$

Where I = current flowing in the diode,

I<sub>0</sub> = reverse saturation current

$V$  = voltage applied to the diode,

$V_T$  = volt- equivalent of temperature =  $k T/q = T/ 11,600 = 26\text{mV}$  (@ room temp)

$\eta=1$  (for Ge) and 2 (for Si)

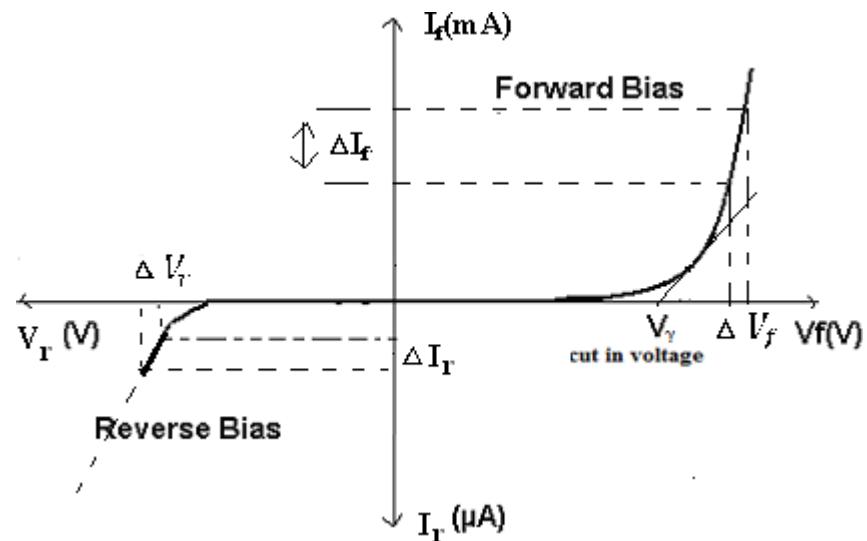

### Ideal Characteristics of Diode:

### Calculations from Graph:

Cutin Voltage  $V_r =$

$$\text{Static forward Resistance } R_{dc} = V_f/I_f \Omega$$

$$\text{Dynamic Forward Resistance } r_{ac} = \Delta V_f/\Delta I_f \Omega$$

$$\text{Static Reverse Resistance } R_{dc} = V_r/I_r \Omega$$

$$\text{Dynamic Reverse Resistance } r_{ac} = \Delta V_r/\Delta I_r \Omega$$

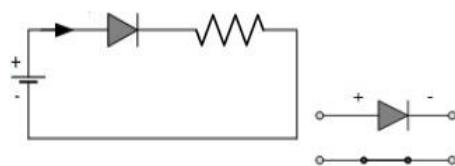

### CIRCUIT DIAGRAM:

Fig. 1: Forward Bias Condition

Fig. 2: Reverse Bias Condition

**PROCEDURE:****(A) FORWARD BIAS CONDITION:**

1. Connect the circuit as shown in Fig.1 (PN Junction diode with milli-ammeter in series with the diode).

2. Initially vary Regulated Power Supply (RPS) voltage  $V_s$  in steps of 0.1 V. Once the current starts increasing vary  $V_s$  in steps of 0.02V and note down the corresponding readings  $V_f$  and  $I_f$ .

3. Tabulate different forward currents obtained for different forward voltages.

4. Plot the V-I characteristics and calculate the resistance levels

5. Compare the theoretical and practical values (cut-in voltage and resistances).

**(B) REVERSE BIAS CONDITION:**

1. Connect the circuit as shown in Fig.2 (Point contact diode in series with micro ammeter).

2. Vary  $V_s$  in the Regulated Power Supply (RPS) gradually in steps of 1V from 0V to 5V and note down the corresponding readings  $V_r$  and  $I_r$ .

3. Tabulate different reverse currents obtained for different reverse voltages.

4. Plot the V-I characteristics and calculate the resistance levels.

5. Compare the theoretical and practical values.

| Forward Bias  |             | Reverse Bias  |                  |

|---------------|-------------|---------------|------------------|

| $V_f$ (volts) | $I_f$ ( mA) | $V_r$ (volts) | $I_r$ ( $\mu$ A) |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

|               |             |               |                  |

**GRAPH:**

**RESULT:**

## EXPERIMENT-2

### HALF WAVE RECTIFIER USING DIODE

**AIM:** To design a Half Wave Rectifier circuit

**APPARATUS:**

Resistors (5 K $\Omega$ ) – 1

Diode (1N4007) – 1

Analog Discovery Kit / ESIM Software / EC Studio Software

Connecting wires

Bread board

**THEORY:**

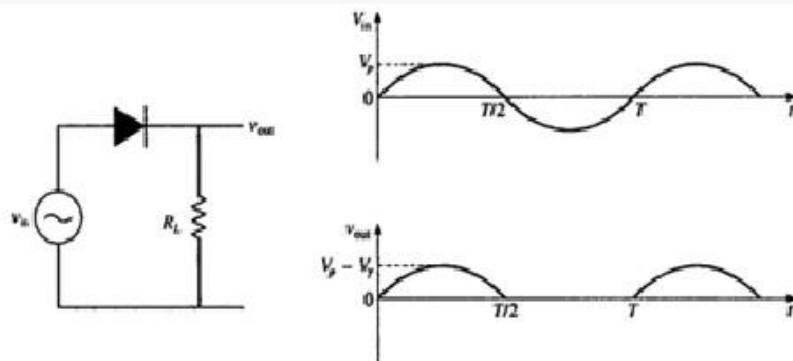

The conversion of AC into DC is called Rectification. Electronic devices can convert AC power into DC power with high efficiency. During the positive half cycle, the diode is forward biased and it conducts and hence a current flow through the load resistor. During the negative half cycle, the diode is reverse biased and it is equivalent to an open circuit, hence the current through the load resistance is zero. Thus the diode conducts only for one half cycle and results in half wave rectification. The input and output voltage waveform may be analytically written as:

$$V_{in} = V_p \sin \omega t, 0 \leq t \leq T$$

and

$$V_{out} = V_{pl} \sin \omega t, 0 \leq t \leq T/2$$

$$V_{out} = 0, T/2 < t \leq T$$

where

$$\text{Peak Value} = V_{pl} = V_p - V_Y$$

and  $V_Y$  is cut-in voltage of the diode.

The average (dc) value of half wave rectified sine wave voltage is represented by

$$V_{avg} = V_{dc} = \frac{V_{pl}}{\pi}$$

RMS voltage at the load resistance can be calculated as

**CIRCUIT DIAGRAM:**

**PROCEDURE:**

1. Connect the circuit as shown in the circuit diagram.

2. Give the input signal as specified.

3. Switch on the power supply.

4. Note down the value of AC and DC voltages from the Waveform software

5. Draw the necessary waveforms on the graph sheet.

**CALCULATIONS:**

$$\text{Average Voltage (V}_{dc}\text{): } V_{ag} = V_d = \frac{V_{pl}}{\pi}$$

$$\text{RMS Voltage (V}_{rms}\text{): } V_{rms} = \frac{V_{pl}}{2}$$

$$\text{Form Factor (FF): } FF = \frac{\text{RMS Value}}{\text{Average Value}} = \frac{V_{RMS}}{V_{dc}}$$

**Ripple Factor:** Ripple factor is defined as the ratio of effective value of AC component to the average DC value. Ripple Factor (r),

$$r = \sqrt{(FF)^2 - 1}$$

$$\text{Efficiency: } \eta = \frac{\text{dc output power}}{\text{ac input power}} = \frac{P_{dc}}{P_{ac}} = \frac{(V_{dc})^2/R_L}{(V_{RMS})^2/R_L}$$

$$\text{Peak Factor: } PF = \frac{\text{Peak Value}}{\text{RMS Value}}$$

**GRAPH:**

**RESULT:**

## EXPERIMENT-3

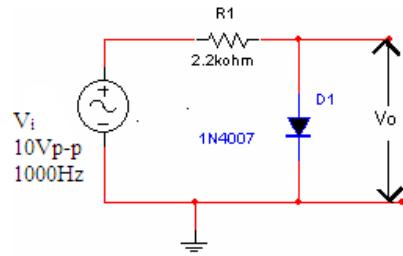

### CLIPPING CIRCUITS

**AIM:** To design Non- linear wave shaping circuits: Clipping Circuits.

#### APPARATUS:

Resistors (2.2 K $\Omega$ ) – 2 Nos

Diode (1N4007) – 2 Nos

Analog Discovery Kit / ESIM Software / EC Studio Software

Connecting wires

Bread board

#### THEORY:

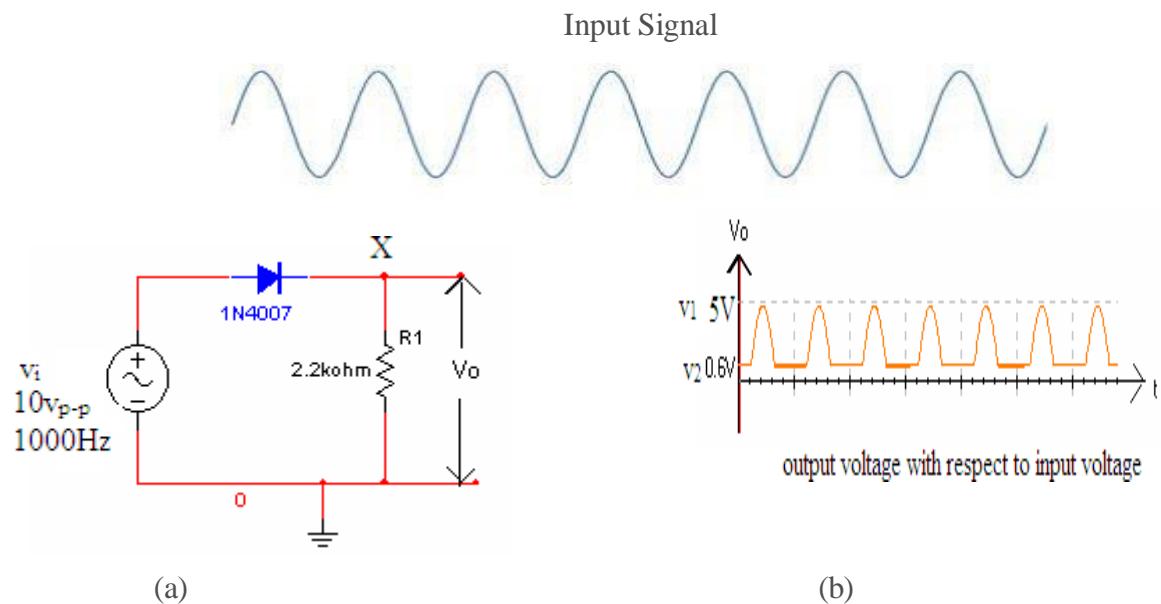

The process whereby the form of sinusoidal signals is going to be altered by transmitting through a non-linear network is called non-linear wave shaping. Non-linear elements (like diodes, transistors) in combination with resistors can function as clipper circuit.

Clipping circuits are used to select transmission of that part of an arbitrary wave form which lies above or below some particular reference voltage level. Clipping circuits are also referred to as Limiters, Amplitude selectors or Slicers.

Clipping circuits are constructed using a combination of resistors, diodes or transistor and reference voltage. Clipping circuits are classified based on the position of diode as

- i. Series diode clipper

- ii. Shunt diode clipper

and further they are classified as, with '0' reference, with +ve reference, with -ve reference; also as positive clipper , negative clipper.

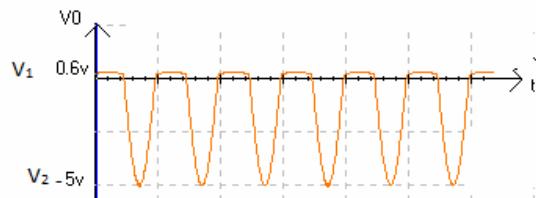

#### PROCEDURE:

1. Connect the circuit as shown in the figures given below.

2. In each case, apply 10 V<sub>P-P</sub>, 1 KHz Sine wave.

3. Observe the Output waveform ( $V_o$  in the circuit) and compare it with Input waveform.

4. Sketch the Input as well as Output waveforms and mark the voltage levels.

5. Note the changes in the Output due to variations in the reference voltage  $V_R = 0V, 2V$ , etc.

6. Repeat the above steps for all the clipping circuits.

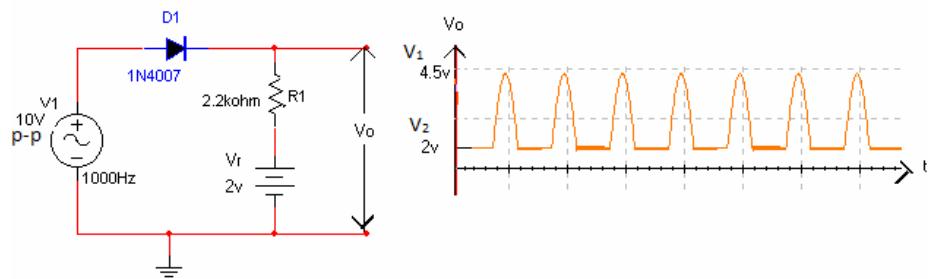

## CIRCUIT DIAGRAMS:

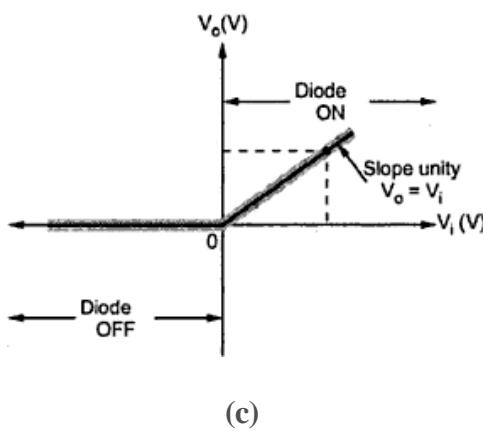

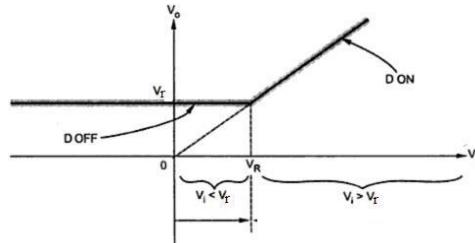

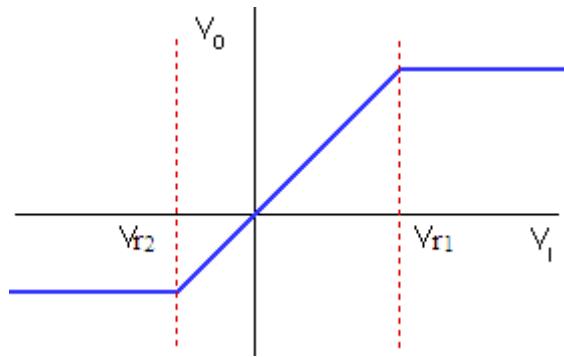

## TRANSFER CHARACTERISTICS:

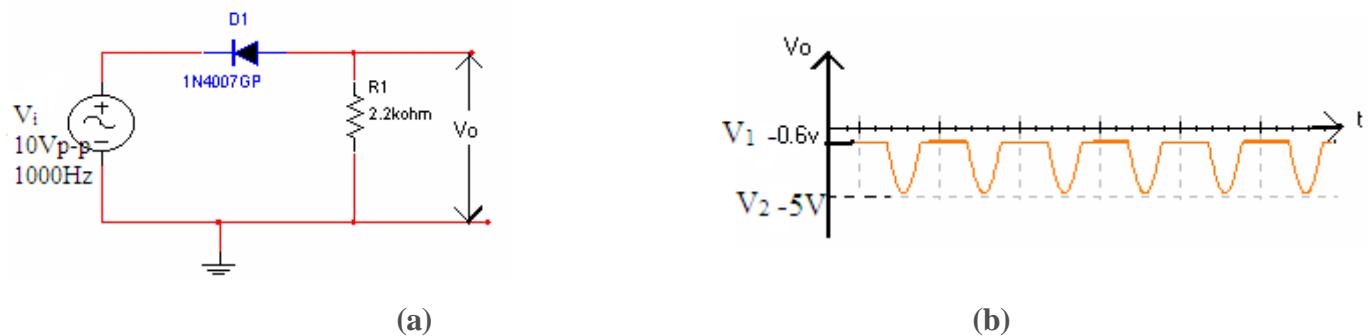

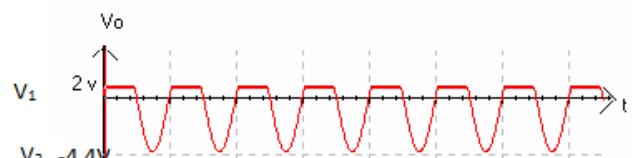

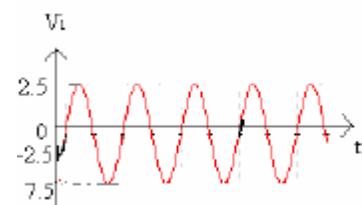

Fig 2.1 (a) Negative clipper with zero reference (Series clipper) (b) Waveforms, (c) Input Voltage vs Output Voltage graph

## TRANSFER CHARACTERISTICS:

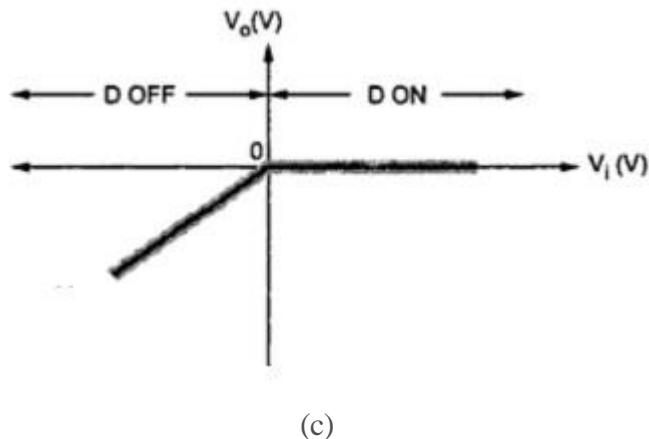

Fig 2.2 (a) Positive clipper with zero reference (Series clipper), (b) Waveforms and (c) Input Voltage vs Output Voltage graph

(a)

(b)

## TRANSFER CHARACTERISTICS:

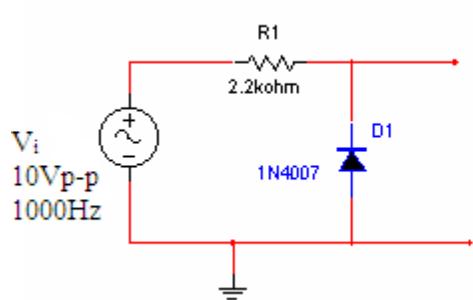

Fig 2.3 (a) Negative clipper with zero reference (Shunt clipper), (b) Waveforms and (c) Input Voltage vs Output Voltage graph

(a)

(b)

### TRANSFER CHARACTERISTICS:

(c)

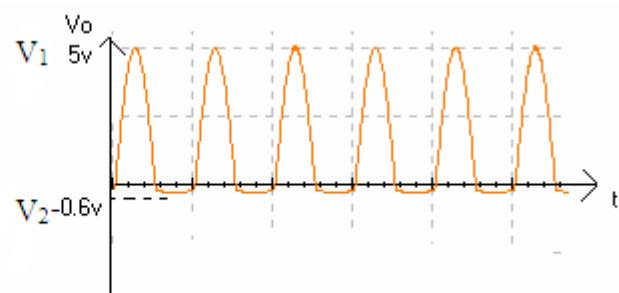

Fig 2.4 (a) Positive clipper with zero reference (Shunt clipper), (b) Waveforms and (c) Input Voltage vs Output Voltage graph

(a)

(b)

### TRANSFER CHARACTERISTICS:

(c)

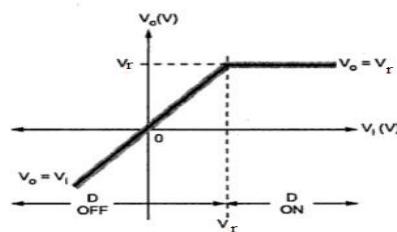

Fig. 2.5 (a) Positive clipper with positive reference (Series clipper) , (b) Waveforms and (c) Input Voltage vs Output Voltage graph

(a)

(b)

**Transfer characteristics:**

(c)

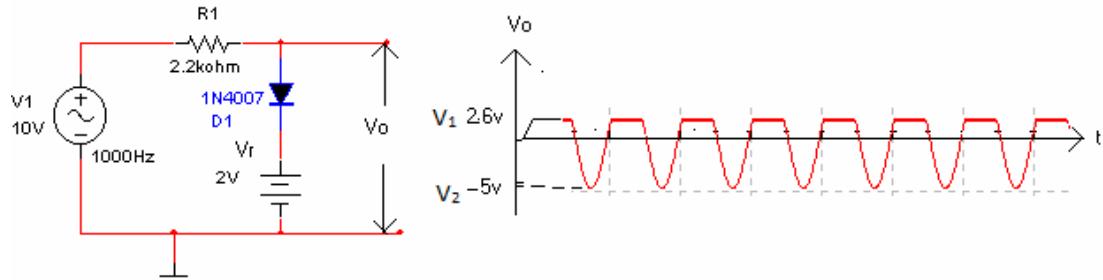

**Fig. 2.6 (a) Positive clipper with positive reference (Shunt clipper), (b) Waveforms and (c) Input Voltage vs Output Voltage graph**

(a)

(b)

**Transfer characteristics:**

(c)

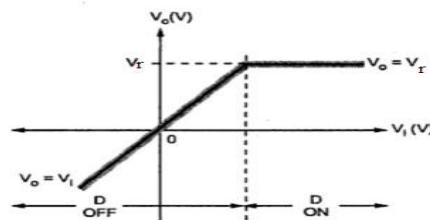

**Fig. 2.7 (a) Negative clipper with positive reference (Series clipper) , (b) Waveforms and (c) Input Voltage vs Output Voltage graph**

**(a)**

**(b)**

**Transfer characteristics:**

**(c)**

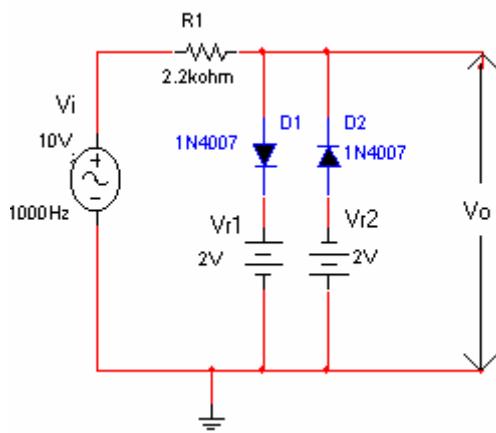

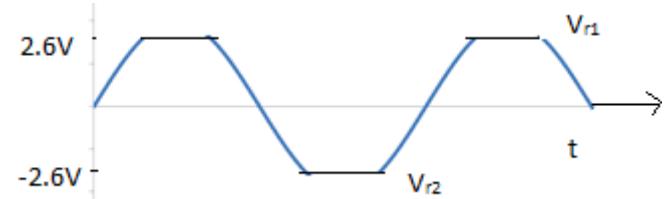

**Fig.2.9 (a) Clipping at two independent levels, (b) Waveforms and (c) Input Voltage vs Output Voltage graph**

**OBSERVATIONS:**

| S.No. | Type of Clipper         | Reference Voltage | Practical Clipping Voltage levels |

|-------|-------------------------|-------------------|-----------------------------------|

| 1     | Series Positive Clipper | 0V                | V1                                |

|       |                         |                   | V2                                |

|       |                         | 2V                | V1                                |

|       |                         |                   | V2                                |

| S.No. | Type of Clipper         | Reference Voltage | Practical Clipping Voltage levels |  |

|-------|-------------------------|-------------------|-----------------------------------|--|

| 2     | Series Negative Clipper | 0V                | V1                                |  |

|       |                         |                   | V2                                |  |

|       |                         | 2V                | V1                                |  |

|       |                         |                   | V2                                |  |

| 3     | Shunt Positive Clipper  | 0V                | V1                                |  |

|       |                         |                   | V2                                |  |

|       |                         | 2V                | V1                                |  |

|       |                         |                   | V2                                |  |

| 4     | Shunt Negative Clipper  | 0V                | V1                                |  |

|       |                         |                   | V2                                |  |

|       |                         | 2V                | V1                                |  |

|       |                         |                   | V2                                |  |

| 5     | Two level clipper       |                   | V1                                |  |

|       |                         |                   | V2                                |  |

**GRAPH:**

**RESULT:**

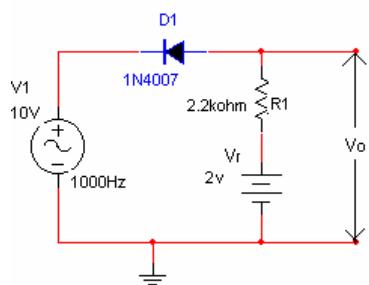

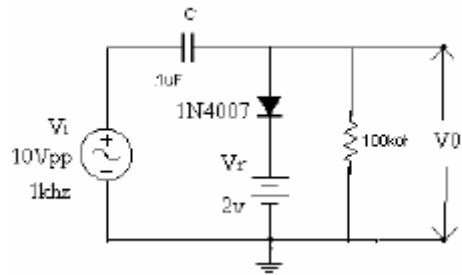

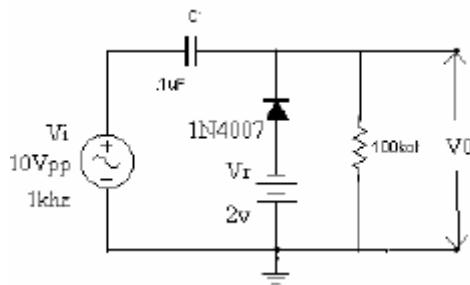

## EXPERIMENT-4

# CLAMPING CIRCUITS

**AIM:** To design Non- linear wave shaping circuits: Clamping circuits.

### APPARATUS:

Resistors ( $100\text{K}\Omega$ ) – 1 No

Diode (1N4007) – 1 No

Capacitor (0.1pF) – 1 No

Analog Discovery Kit / ESIM Software / EC Studio Software

Connecting wires

Bread board

### Theory:

The process where sinusoidal signals are going to be altered by transmitting through a non-linear network is called non-linear wave shaping. Non-linear elements (like diodes) in combination with resistors and capacitors can function as clamping circuit.

Clamping circuits add a DC level to an AC signal. A clumper is also referred to as DC restorer or DC re-inserter. The Clampers clamp the given waveform either above or below the reference level, which are known as positive or negative clampers respectively.

Clamping circuits are classified as two types.

- i. Negative Clampers

- ii. Positive Clampers

### Procedure:

1. Connect the circuit as shown in the figure 3.1 below.

2. Apply a Sine wave of 10V P-P, 1KHz at the input terminals.

3. Observe the I/P & O/P waveforms on CRO and plot the waveforms and mark the values with  $V_R = 0\text{V}$ ,  $3\text{V}$ , etc.

4. Output is taken across the load  $RL$ .

5. Repeat the above steps for all clamping circuits ( fig 3.2 to fig 3.6) as shown.

6. Draw the waveforms, assuming the diode is practical.

### Circuit diagrams:

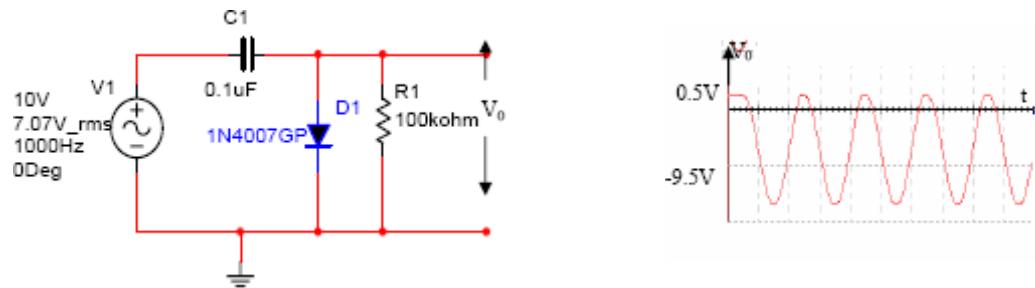

Fig.3.1 Negative clamping with zero reference voltage

Fig.3.2 positive clamping with zero reference voltage

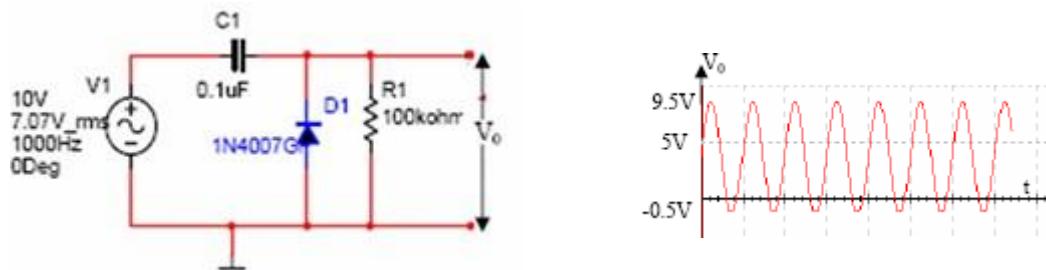

Fig.3.3 Negative clamping with Negative reference voltage

Fig.3.4 positive clamping positive reference voltage

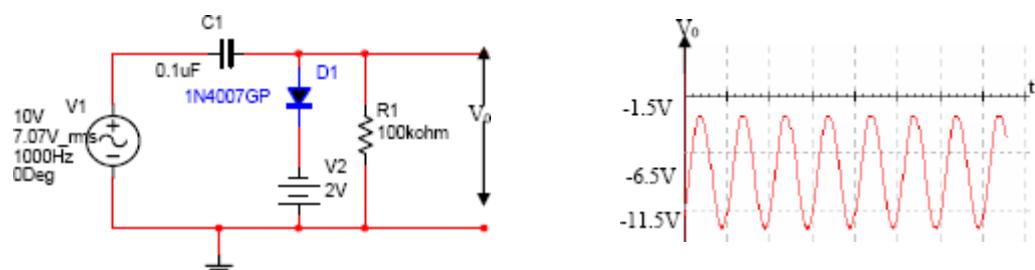

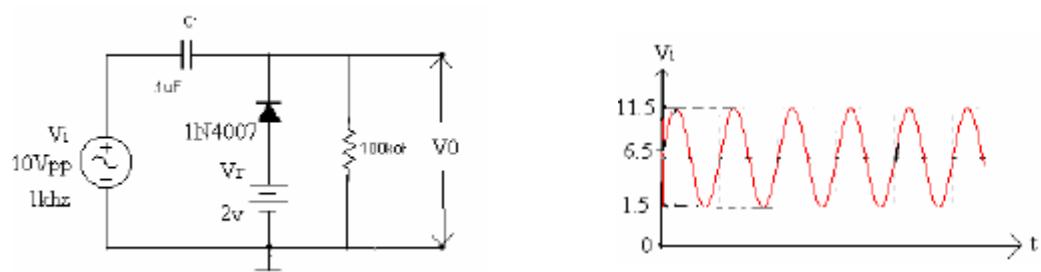

Fig.3.5 Negative clamping with Positive reference voltage

Fig.3.6 Positive clamping with Negative reference voltage

### Observations:

| S.No. | Type of Clamper  | Ref. Voltage | Practicle clamping ref.voltage levels |  |

|-------|------------------|--------------|---------------------------------------|--|

| 1.    | Positive Clamper | 0V           | V1                                    |  |

|       |                  |              | V2                                    |  |

|       |                  | 2V           | V1                                    |  |

|       |                  |              | V2                                    |  |

|       |                  | -2V          | V1                                    |  |

|       |                  |              | V2                                    |  |

| 2.    | Negative Clamper | 0V           | V1                                    |  |

|       |                  |              | V2                                    |  |

|       |                  | 2V           | V1                                    |  |

|       |                  |              | V2                                    |  |

|       |                  | -2V          | V1                                    |  |

|       |                  |              | V2                                    |  |

**GRAPH:**

**RESULT:**

## EXPERIMENT-5

### BJT Input and Output Characteristics

**AIM:** To study BJT CE (Common Emitter) and CB (Common Base) Configurations

#### APPARATUS:

BJT (NPN) – CK 100 or its equivalent – 1 No.

BJT (PNP) – BC 107 or its equivalent – 1 No.

Resistors –  $2.2\text{K}\Omega$  – 2 No(s).

Analog Discovery Kit / ESIM Software / EC Studio Software

Connecting wires

Bread board

#### THEORY:

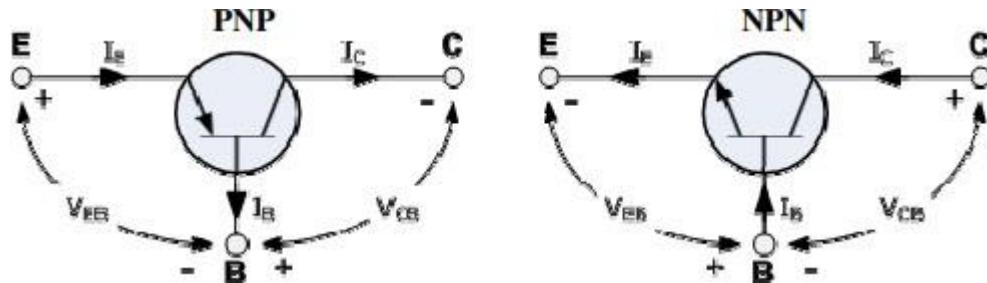

A Bipolar Junction Transistor, or BJT is a three terminal device having two PN-junctions connected together in series. Each terminal is given a name to identify it and these are known as the Emitter (E), Base (B) and Collector (C). There are two basic types of bipolar transistor construction, NPN and PNP, which basically describes the physical arrangement of the Ptype and N-type semiconductor materials from which they are made. Bipolar Transistors are "CURRENT" Amplifying or current regulating devices that control the amount of current flowing through them in proportion to the amount of biasing current applied to their base terminal. The principle of operation of the two transistor types NPN and PNP, is exactly the same the only difference being in the biasing (base current) and the polarity of the power supply for each type.

The symbols for both the NPN and PNP bipolar transistor are shown above along with the direction of conventional current flow. The direction of the arrow in the symbol shows current flow between the base and emitter terminal, pointing from the positive P-type region to the negative N-type region, like the standard diode symbol. For normal operation, the emitter-base junction is forward-biased, and the collector-base junction is reverse-biased. **Transistor Configurations** There are three possible configurations possible when a transistor is connected in a circuit: (a) Common base, (b) Common emitter (c) Common collector. We will be focusing on the first two configurations in this experiment. The behavior of a transistor can be represented by d.c. current-voltage (I-V) curves, called the static characteristic curves of the device. The three important characteristics of a transistor are: (i) Input characteristics, (ii) Output characteristics and (iii) Transfer Characteristics. These characteristics give information about various transistor parameters, e.g., input and out dynamic resistance, current amplification factors, etc.

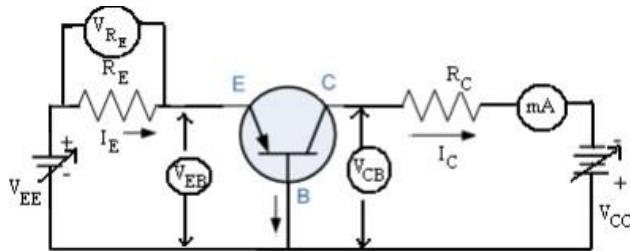

## Common Base Transistor Characteristics

In common base configuration, the base is made common to both input and output as shown in its circuit diagram.

**(1) Input Characteristics:** The input characteristics is obtained by plotting a curve between  $I_E$  and  $V_{EB}$  keeping voltage  $V_{CB}$  constant. This is very similar to that of a forward-biased diode and the slope of the plot at a given operating point gives information about its input dynamic resistance.

**Input Dynamic Resistance ( $r_i$ )** This is defined as the ratio of change in base emitter voltage ( $\Delta V_{EB}$ ) to the resulting change in emitter current ( $\Delta I_E$ ) at constant collector-emitter voltage ( $V_{CB}$ ). This is dynamic as its value varies with the operating current in the transistor.

$$r_i = \left. \frac{\Delta V_{EB}}{\Delta I_E} \right|_{V_{CB}}$$

**(2) Output Characteristics:** The output characteristic curves are plotted between  $I_C$  and  $V_{CB}$ , keeping  $I_E$  constant. The output characteristics are controlled by the input characteristics. Since  $I_C$  changes with  $I_E$ , there will be different output characteristics corresponding to different values of  $I_E$ . These curves are almost horizontal. This shows that the output dynamic resistance, defined below, is very high.

**Output Dynamic Resistance ( $r_o$ ):** This is defined as the ratio of change in collector-base voltage ( $\Delta V_{CB}$ ) to the change in collector current ( $\Delta I_C$ ) at a constant base current  $I_E$ .

$$r_o = \left. \frac{\Delta V_{CB}}{\Delta I_C} \right|_{I_E}$$

**(3) Transfer Characteristics:** The transfer characteristics are plotted between the input and output currents ( $I_E$  versus  $I_C$ ).

## Current amplification factor ( $\alpha$ )

This is defined as the ratio of the change in collector current to the change in emitter current at a constant collector-base voltage ( $V_{CB}$ ) when the transistor is in active state.

$$\alpha_{ac} = \left. \frac{\Delta I_C}{\Delta I_E} \right|_{V_{CB}}$$

This is also known as small signal current gain and its value is very large. The ratio of  $I_C$  and  $I_E$  is called  $\alpha_{dc}$  of the transistor. Hence,

$$\alpha_{dc} = \left. \frac{I_C}{I_E} \right|_{V_{CB}}$$

Since  $I_C$  increases with  $I_E$  almost linearly, the values of both  $\alpha_{dc}$  and  $\alpha_{ac}$  are nearly equal.

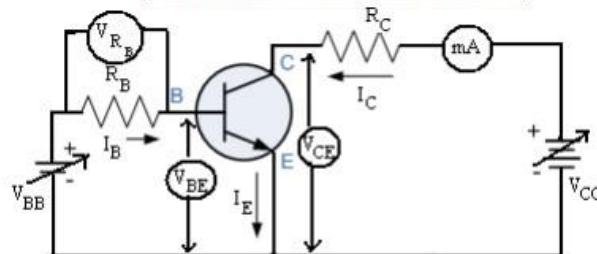

### Common Emitter Transistor Characteristics:

In a common emitter configuration, emitter is common to both input and output as shown in its circuit diagram.

**(1) Input Characteristics:** The variation of the base current  $I_B$  with the base-emitter voltage  $V_{BE}$  keeping the collector-emitter voltage  $V_{CE}$  fixed, gives the input characteristic in CE mode.

**Input Dynamic Resistance ( $r_i$ ):** This is defined as the ratio of change in base emitter voltage ( $\Delta V_{BE}$ ) to the resulting change in base current ( $\Delta I_B$ ) at constant collector-emitter voltage ( $V_{CE}$ ). This is dynamic and it can be seen from the input characteristic, its value varies with the operating current in the transistor:

$$r_i = \left. \frac{\Delta V_{BE}}{\Delta I_B} \right|_{V_{CE}}$$

The value of  $r_i$  can be anything from a few hundreds to a few thousand ohms.

**(2) Output Characteristics:** The variation of the collector current  $I_C$  with the collector-emitter voltage  $V_{CE}$  is called the output characteristic. The plot of  $I_C$  versus  $V_{CE}$  for different fixed values of  $I_B$  gives one output characteristic. Since the collector current changes with the base current, there will be different output characteristics corresponding to different values of  $I_B$ .

**Output Dynamic Resistance ( $r_o$ ):** This is defined as the ratio of change in collector-emitter voltage ( $\Delta V_{CE}$ ) to the change in collector current ( $\Delta I_C$ ) at a constant base current  $I_B$ .

$$r_o = \left. \frac{\Delta V_{CE}}{\Delta I_C} \right|_{I_B}$$

The high magnitude of the output resistance (of the order of 100 kW) is due to the reverse biased state of this diode.

**(3) Transfer Characteristics:** The transfer characteristics are plotted between the input and output currents ( $I_B$  versus  $I_C$ ). Both  $I_B$  and  $I_C$  increase proportionately.

**Current amplification factor ( $\beta$ ):** This is defined as the ratio of the change in collector current to the change in base current at a constant collector-emitter voltage ( $V_{CE}$ ) when the transistor is in active state.

$$\beta_{ac} = \left. \frac{\Delta I_C}{\Delta I_B} \right|_{V_{CE}}$$

This is also known as small signal current gain and its value is very large. The ratio of  $I_C$  and  $I_B$  we get what is called  $\beta_{dc}$  of the transistor. Hence,

$$\beta_{dc} = \left. \frac{I_C}{I_B} \right|_{V_{CE}}$$

Since  $I_C$  increases with  $I_B$  almost linearly, the values of both  $\beta_{dc}$  and  $\beta_{ac}$  are nearly equal.

### CIRCUIT DIAGRAM:

PNP transistor in CB configuration

NPN transistor in CE configuration

### PROCEDURE:

1. Note down the type number of both the transistors.

2. Identify different terminals (E, B and C) and the type (PNP/NPN) of the transistors. For any specific information refer the datasheet of the transistors.

#### (I) PNP Common Base (CB) characteristics

1. Configure CB circuit using the PNP transistor as per the circuit diagram. Use  $R_E = R_C = 150 \Omega$ .

2. For input characteristics, first fix the voltage  $V_{CB}$  by adjusting  $V_{CC}$  to the minimum possible position. Now vary the voltage  $V_{EB}$  slowly (say, in steps of 0.05V) by varying  $V_{EE}$ . Measure  $V_{EB}$  using a AD Kit. If  $V_{CB}$  varies during measurement bring it back to the initial set value To determine  $I_E$ , measure  $V_{RE}$  across the resistor  $R_E$  and use the relation  $I_E = V_{RE}/R_E$ .

3. Repeat the above step for another value of  $V_{CB}$  say, 2V.

4. Take out the AD Kit at  $V_{EB}$  and connect in series with the output circuit to measure  $I_C$ . For output characteristics, first fix  $I_E = 0$ , i.e.  $V_{RE} = 0$ . By adjusting  $V_{CC}$ , vary the collector voltage  $V_{CB}$  in steps of say 1V and measure  $V_{CB}$  and the corresponding  $I_C$  using AD Kits. After acquiring sufficient readings, bring back  $V_{CB}$  to 0 and reduce it further to get negative values. Vary  $V_{CB}$  in negative direction and measure both  $V_{CB}$  and  $I_C$ , till you get 0 current.

5. Repeat the above step for at least 5 different values of  $I_E$  by adjusting  $V_{EE}$ . You may need to adjust  $V_{EE}$  continuously during measurement to maintain a constant  $I_E$ .

6. Plot the input and output characteristics by using the readings taken above and determine the input and output dynamic resistance.

7. To plot transfer characteristics, select a suitable voltage  $V_{CB}$  well within the active region of the output characteristics, which you have tabulated already. Plot a graph between  $I_C$  and the corresponding  $I_E$  at the chosen voltage  $V_{CB}$ . Determine  $\alpha_{ac}$  from the slope of this graph.

## (II) NPN Common Emitter (CE) characteristics

1. Now configure CE circuit using the NPN transistor as per the circuit diagram. Use  $R_B = 100\text{k}\Omega$  and  $R_C = 1\text{k}\Omega$ .

2. For input characteristics, first fix the voltage  $V_{CE}$  by adjusting  $V_{CC}$  to the minimum possible position. Now vary the voltage  $V_{BE}$  slowly (say, in steps of 0.05V) by varying  $V_{BB}$ . Measure  $V_{BE}$  using AD Kit. If  $V_{CE}$  varies during measurement bring it back to the set value to determine  $I_B$ , measure  $V_{RB}$  across the resistor  $R_B$  and use the relation  $I_B = V_{RB}/R_B$ .

3. Repeat the above step for another value of  $V_{CE}$  say, 2V.

4. For output characteristics, first fix  $I_B = 0$ , i.e.  $V_{RB} = 0$ . By adjusting  $V_{CC}$ , vary the collector voltage  $V_{CE}$  in steps of say 1V and measure  $V_{CE}$  and the corresponding  $I_C$  using AD Kit. If needed vary  $V_{CE}$  in negative direction as described for CB configuration and measure both  $V_{CE}$  and  $I_C$ , till you get 0 current.

5. Repeat the above step for at least 5 different values of  $I_B$  by adjusting  $V_{BB}$ . You may need to adjust  $V_{BB}$  continuously during measurement to maintain a constant  $I_B$ .

6. Plot the input and output characteristics by using the readings taken above and determine the input and output dynamic resistance.

7. Plot the transfer characteristics between  $I_C$  and  $I_B$  as described for CB configuration for a suitable voltage of  $V_{CE}$  on the output characteristics. Determine  $\beta_{ac}$  from the slope of this graph.

### Observations:

#### CB configuration:

Transistor code: \_\_\_\_\_, Transistor type: \_\_\_\_\_ (PNP/NPN)  $R_E = \underline{\hspace{2cm}}$ ,  $R_C = \underline{\hspace{2cm}}$ .

#### Table (1): Input Characteristics

| S. No | $V_{CB} = \underline{\hspace{2cm}} \text{V}$ |                     |                   | $V_{CB} = \underline{\hspace{2cm}} \text{V}$ |                     |                   |

|-------|----------------------------------------------|---------------------|-------------------|----------------------------------------------|---------------------|-------------------|

|       | $V_{EB} (\text{V})$                          | $V_{RE} (\text{V})$ | $I_E (\text{mA})$ | $V_{EB} (\text{V})$                          | $V_{RE} (\text{V})$ | $I_E (\text{mA})$ |

|       |                                              |                     |                   |                                              |                     |                   |

|       |                                              |                     |                   |                                              |                     |                   |

|       |                                              |                     |                   |                                              |                     |                   |

|       |                                              |                     |                   |                                              |                     |                   |

|       |                                              |                     |                   |                                              |                     |                   |

|       |                                              |                     |                   |                                              |                     |                   |

#### Table (2): Output Characteristics

| S. NO | $I_{E1} = 0$        |                   | $I_{E2} = \underline{\hspace{2cm}}$ |                   | $I_{E3} = \underline{\hspace{2cm}}$ |                   | $I_{E4} = \underline{\hspace{2cm}}$ |                   | $I_{E5} = \underline{\hspace{2cm}}$ |                   |

|-------|---------------------|-------------------|-------------------------------------|-------------------|-------------------------------------|-------------------|-------------------------------------|-------------------|-------------------------------------|-------------------|

|       | $V_{CB} (\text{V})$ | $I_C (\text{mA})$ | $V_{CB} (\text{V})$                 | $I_C (\text{mA})$ | $V_{CB} (\text{V})$                 | $I_C (\text{mA})$ | $V_{CB} (\text{V})$                 | $I_C (\text{mA})$ | $V_{CB} (\text{V})$                 | $I_C (\text{mA})$ |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

|       |                     |                   |                                     |                   |                                     |                   |                                     |                   |                                     |                   |

**Table (3): Transfer Characteristics:  $V_{CB} = \underline{\hspace{2cm}} V$**

## CE configuration:

Transistor code: \_\_\_\_\_, Transistor type: \_\_\_\_\_ (PNP/NPN)  $R_B$  = \_\_\_\_\_,  $R_C$  = \_\_\_\_\_.

**Table (1): Input Characteristics**

| S. No | V <sub>CE</sub> =_____ V |                     |                     | V <sub>CE</sub> =_____ V |                     |                     |

|-------|--------------------------|---------------------|---------------------|--------------------------|---------------------|---------------------|

|       | V <sub>BE</sub> (V)      | V <sub>RB</sub> (V) | I <sub>B</sub> (μA) | V <sub>BE</sub> (V)      | V <sub>RB</sub> (V) | I <sub>B</sub> (μA) |

|       |                          |                     |                     |                          |                     |                     |

|       |                          |                     |                     |                          |                     |                     |

|       |                          |                     |                     |                          |                     |                     |

|       |                          |                     |                     |                          |                     |                     |

|       |                          |                     |                     |                          |                     |                     |

**Table (2): Output Characteristics**

**Table (3): Transfer Characteristics:**  $V_{CE} = \underline{\hspace{2cm}} V$

| S. NO | $I_B(\mu A)$ | $I_C(mA)$ |

|-------|--------------|-----------|

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

|       |              |           |

**Graphs:** Plot the input, output and transfer characteristics for each configuration.

**CB configuration:**

- (1) **Input characteristics:** Plot  $V_{EB} \sim I_E$ , for different  $V_{CB}$  and determine the input dynamic resistance in each case at suitable operating points.

- (2) **Output characteristics:** Plot  $V_{CB} \sim I_C$ , for different  $I_E$  and determine the output dynamic resistance in each case at suitable operating points in the active region.

- (3) **Transfer characteristics:** Plot  $I_E \sim I_C$ , for a fixed  $V_{CB}$  and determine  $\alpha_{ac}$ .

**CE configuration:**

- (1) **Input characteristics:** Plot  $V_{BE} \sim I_B$ , for different  $V_{CE}$  and determine the input dynamic resistance in each case at suitable operating points.

- (2) **Output characteristics:** Plot  $V_{CE} \sim I_C$ , for different  $I_B$  and determine the output dynamic resistance in each case at suitable operating points in the active region.

- (3) **Transfer characteristics:** Plot  $I_B \sim I_C$ , for a fixed  $V_{CE}$  and determine  $\beta_{ac}$ .

**GRAPH:**

**RESULT:**

## EXPERIMENT-7

### JFET Characteristics

#### AIM:

To study Drain Characteristics of a Junction Field Effect Transistor (JFET).

#### APPARATUS:

JFET (2N547N or its equivalent) – 1

No.

Resistor ( $1\text{K}\Omega$ ,  $100\text{K}\Omega$ )

Analog Discovery Kit/ESIM Software / EC Studio

Software Connecting wires

Bread board

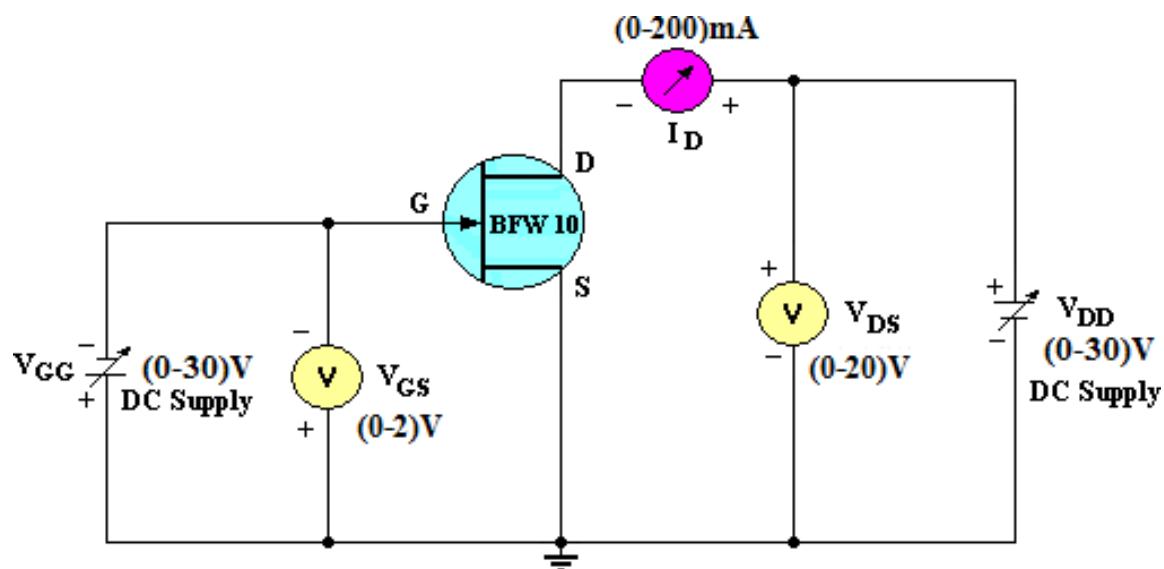

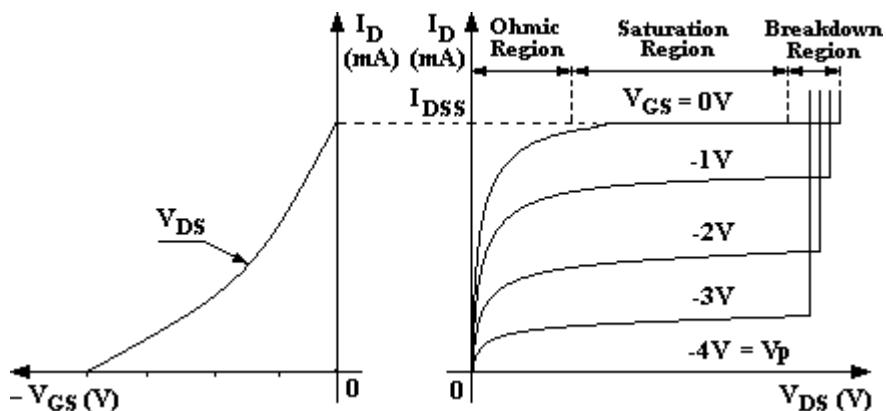

#### CIRCUIT DIAGRAM:

#### MODEL GRAPH:

FET Transfer Characteristics

FET Drain Characteristics

## THEORY:

### Introduction:

The field effect transistor (FET) is made of a bar of N type material called the SUBSTRATE with a P type junction (the gate) diffused into it. With a positive voltage on the drain, with respect to the source, electron current flows from source to drain through the CHANNEL.

If the gate is made negative with respect to the source, an electrostatic field is created which squeezes the channel and reduces the current. If the gate voltage is high enough the channel will be "pinched off" and the current will be zero. The FET is voltage controlled, unlike the transistor which is current controlled. This device is sometimes called the junction FET or IGFET or JFET.

If the FET is accidentally forward biased, gate current will flow and the FET will be destroyed. To avoid this, an extremely thin insulating layer of silicon oxide is placed between the gate and the channel and the device is then known as an insulated gate FET, or IGFET or metal oxide semiconductor FET (MOSFET). Drain characteristics are obtained between the drain to source voltage ( $V_{DS}$ ) and drain current ( $I_D$ ) taking gate to source voltage ( $V_{GS}$ ) as the parameter. Transfer characteristics are obtained between the gate to source voltage ( $V_{GS}$ ) and Drain current ( $I_D$ ) taking drain to source voltage ( $V_{DS}$ ) as parameter.

## PROCEDURE:

### DRAIN CHARACTERISTICS:

1. Connect the circuit as per the Fig. 1 and start with  $V_{GG}$  and  $V_{DD}$  keeping at zero volts.

2. Keep  $V_{GG}$  such that  $V_{GS} = 0$  volts, Now vary  $V_{DD}$  such that  $V_{DS}$  varies in steps of 1 volt up to 10 volts. And Note down the corresponding Drain current  $I_D$

3. Repeat the above experiment with  $V_{GS} = -1V$  and  $-2V$  and tabulate the readings.

4. Draw a graph  $V_{DS}$  Vs  $I_D$  against  $V_{GS}$  as parameter on graph.

5. From the above graph calculate  $r_d$  and note down the corresponding diode current against the voltage in the tabular form.

6. Draw the graph between voltage across the Diode Vs Current through the diode in the first quadrant as shown in fig.

**TABULAR FORM:**

**DRAIN CHARACTERISTICS:**

| S.No |              | $V_{GS} = 0$ volts | $V_{GS} = -1V$ | $V_{GS} = -2V$ |

|------|--------------|--------------------|----------------|----------------|

|      | $V_{DS}$ (V) | $I_D$ (mA)         | $I_D$ (mA)     | $I_D$ (mA)     |

| 1    |              |                    |                |                |

| 2    |              |                    |                |                |

| 3    |              |                    |                |                |

| 4    |              |                    |                |                |

| 5    |              |                    |                |                |

| 6    |              |                    |                |                |

| 7    |              |                    |                |                |

| 8    |              |                    |                |                |

| 9    |              |                    |                |                |

| 10   |              |                    |                |                |

| 11   |              |                    |                |                |

| 12   |              |                    |                |                |

| 13   |              |                    |                |                |

## EXPERIMENT: 8

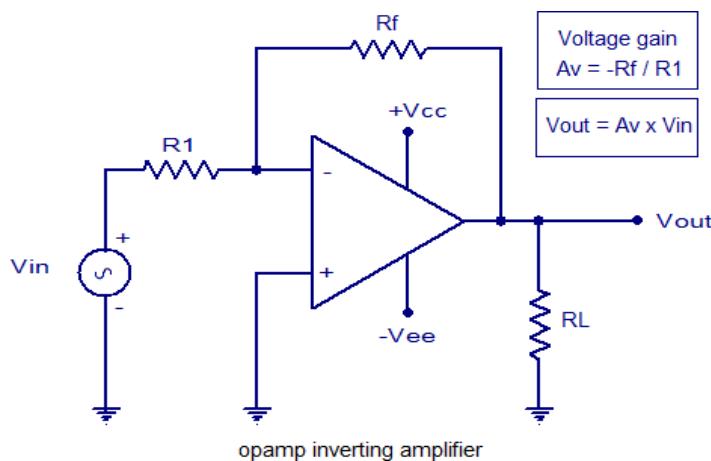

### INVERTING AMPLIFIER

**AIM:** To design an Inverting Amplifier Circuit using Op-Amp.

**APPARATUS:** LM324AD/741/OP27 IC or its equivalent

$R_f$ ,  $R_1$  resistors (select  $R_f$  and  $R_1$  such that  $R_f \gg R_1$ )

Analog Discovery Kit (AD Kit) / ESIM Software / EC Studio Software

Connecting wires

Breadboard

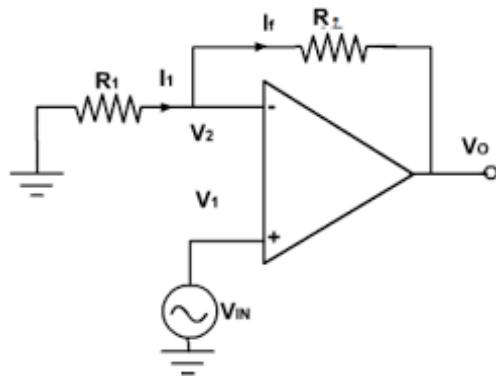

#### CIRCUIT DIAGRAM:

**Figure: Inverting Amplifier**

#### THEORY:

As the open loop DC gain of an [Operational Amplifiers](#) is extremely high we can therefore afford to lose some of this high gain by connecting a suitable resistor across the amplifier from the output terminal back to the inverting input terminal to both reduce and control the overall gain of the amplifier. This then produces and effect known commonly as [Negative Feedback](#), and thus produces a very stable Operational Amplifier based system.

Negative Feedback is the process of “feeding back” a fraction of the output signal back to the input, but to make the feedback negative, we must feed it back to the negative or “inverting input” terminal of the op-amp using an external Feedback Resistor called  $R_f$ . This feedback connection between the output and the inverting input terminal forces the differential input voltage towards zero.

This effect produces a closed loop circuit to the amplifier resulting in the gain of the amplifier now being called its Closed-loop Gain. Then a closed-loop inverting amplifier uses negative feedback to accurately control the overall gain of the amplifier, but at a cost in the reduction of the amplifiers gain. This negative feedback results in the inverting input terminal having a different signal on it than the actual input voltage as it will be the sum of the input voltage plus the negative feedback voltage

giving it the label or term of a *Summing Point*. We must therefore separate the real input signal from the inverting input by using an Input Resistor,  $R_{in}$ .

In this Inverting Amplifier circuit the operational amplifier is connected with feedback to produce a closed loop operation. When dealing with operational amplifiers there are two very important rules to remember about inverting amplifiers, these are: “No current flows into the input terminal” and that “ $V_1$  always equals  $V_2$ ”. However, in real world op-amp circuits both of these rules are slightly broken.

This is because the junction of the input and feedback signal (  $X$  ) is at the same potential as the positive ( + ) input which is at zero volts or ground then, the junction is a “Virtual Earth”. Because of this virtual earth node the input resistance of the amplifier is equal to the value of the input resistor,  $R_{in}$  and the closed loop gain of the inverting amplifier can be set by the ratio of the two external resistors.

We said above that there are two very important rules to remember about Inverting Amplifiers or any operational amplifier for that matter and these are.

1. No Current Flows into the Input Terminals

2. The Differential Input Voltage is Zero as  $V_1 = V_2 = 0$  (Virtual Earth)

$$V_{out} = -\frac{R_f}{R_{in}} \times V_{in}$$

#### PROCEDURE:

1. Connect the components as per the circuit diagram on the Bread board

2. The color terminals represent the connections made with respect to the Analog Discovery kit at the respective terminals on the Bread board

3. Adjust the input voltage starting with 500mv and find the output voltage.

4. Repeat the above steps for different voltages by taking different input signals

5. Draw the graph between input and output voltages for the values obtained from the table.

#### TABULAR COLUMN:

| S. No | $V_{in}$ | $V_{out}$ | $V_{out}/V_{in}$ |

|-------|----------|-----------|------------------|

|       |          |           |                  |

|       |          |           |                  |

|       |          |           |                  |

**Theoretical Calculations:**

**MODEL GRAPH:**

**GRAPH SHEET:**

**RESULT:**

**EXERCISE:**

1. Execute the following “Non inverting Amplifier” circuit with different values of  $R_f$  resistances.

2. List the applications of Inverting and Non Inverting Amplifier.

**GRAPH SHEET:**

**RESULT:**

## EXPERIMENT: 9

### SUBTRACTOR CIRCUIT

**AIM:** To design a Subtractor Circuit using Op-Amp.

**APPARATUS:** LM324AD/741/OP27 IC or its equivalent

Resistors 2.2K $\Omega$ , 10K $\Omega$

Analog Discovery Kit (AD Kit) / ESIM Software / EC Studio Software

Connecting Wires, Breadboard

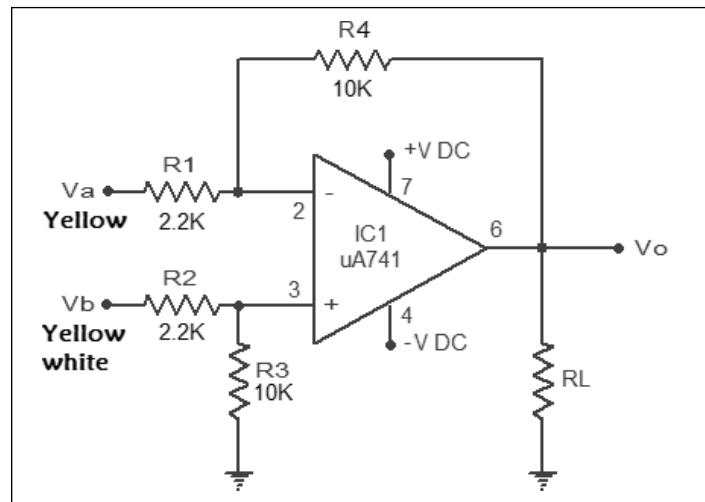

#### CIRCUIT DIAGRAM:

**Figure: Subtractor/Difference Circuit**

#### THEORY:

The *differential amplifiers* amplify the difference between two voltages making this type of operational amplifier circuit a Subtractor unlike a summing amplifier which adds or sums together the input voltages. This type of operational amplifier circuit is commonly known as a Differential Amplifier configuration.

By connecting each input in turn to 0v ground we can use superposition to solve for the output voltage  $V_{out}$ . Then the transfer function for a Differential Amplifier circuit is given as:

$$V_{out} = -V_1 \left( \frac{R_3}{R_1} \right) + V_2 \left( \frac{R_4}{R_2 + R_4} \right) \left( \frac{R_1 + R_3}{R_1} \right)$$

When resistors,  $R_1 = R_2$  and  $R_3 = R_4$  the above transfer function for the differential amplifier can be simplified to the following expression:

$$V_{\text{OUT}} = \frac{R_3}{R_1} (V_2 - V_1)$$

If all the resistors are all of the same ohmic value, that is:  $R_1 = R_2 = R_3 = R_4 = R$  then the circuit will become a **Unity Gain Differential Amplifier** and the voltage gain of the amplifier will be exactly one or unity. Then the output expression would simply be  $V_{\text{out}} = V_2 - V_1$ . Also note that if input  $V_1$  is higher than input  $V_2$  the output voltage sum will be negative, and if  $V_2$  is higher than  $V_1$ , the output voltage sum will be positive.

The Differential Amplifier circuit is a very useful op-amp circuit and by adding more resistors in parallel with the input resistors  $R_1$  and  $R_3$ , the resultant circuit can be made to either “Add” or “Subtract” the voltages applied to their respective inputs. One of the most common ways of doing this is to connect a “Resistive Bridge” commonly called a *Wheatstone Bridge*.

#### PROCEDURE:

1. Connect the relevant circuit for the difference configuration as shown in the circuit diagram.

2. Measure the output voltage  $V_o$  from AD Kit.

3. Observe the waveforms at  $V_1$ ,  $V_2$ , and  $V_o$ .

4. Note the phase of the output voltage  $V_o$  with respect to the input voltage.

5. Set different values of two input voltages, and find the output voltage

6. Repeat the steps 3, 4, and 5.

7. The waveforms are to be plotted.

#### TABULAR COLUMN:

| S.No | $V_{\text{in}1}$ | $V_{\text{in}2}$ | $V_{\text{out}}$ |

|------|------------------|------------------|------------------|

|      |                  |                  |                  |

|      |                  |                  |                  |

#### THEORITICAL CALCULATIONS:

**GRAPH SHEET:****RESULT:**

**Exercise:** Derive the expression for the Difference Amplifier. List the applications of Differential amplifier.

## EXPERIMENT: 10

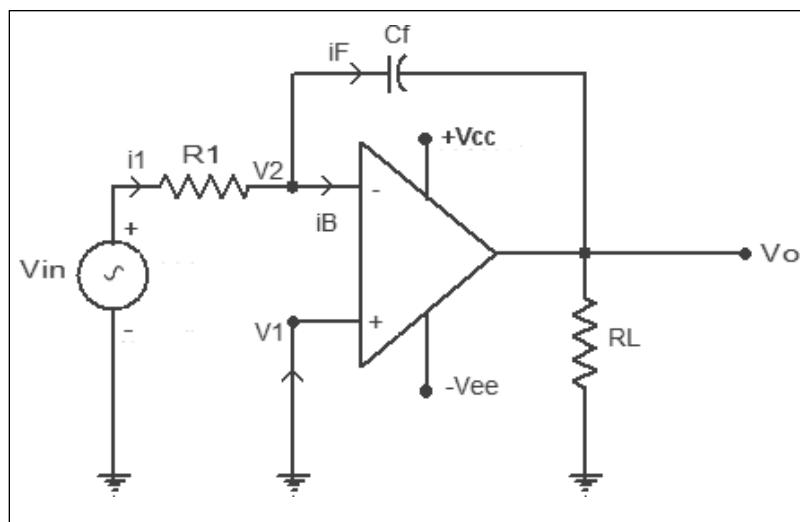

### INTEGRATOR CIRCUIT

**AIM:** To design an Integrator Circuit using Op-Amp

**APPARATUS:** LM324AD/741/OP27 IC or its equivalent

10 K $\Omega$ , 1K $\Omega$  Resistor

100nF Capacitor

Analog Discovery Kit (AD Kit) / ESIM Software / EC Studio Software

Breadboard

#### CIRCUIT DIAGRAM:

Figure: shows the Integrator

#### THEORY:

It is a low pass RC filter circuit. It can work as an integrator when time constant is very large. This requires very large values of R and C by Miller's theorem the effective input capacitance becomes  $C!(1-Av)$  where  $Av$  is the gain of the op-amp. The gain  $Av$  is infinite for an ideal op-amp. so, the effective time constant of the op-amp becomes large which results in perfect integration. The output voltage of an integrator is shown below

$$V_o = \frac{-1}{R_1 C_f} \int_0^t V_{in} dt + C$$

### PROCEDURE:

1. Connect the circuit as shown in the circuit diagram.

2. Suitable  $R_f$  and  $C_1$  are chosen such that the output of the circuit is the integral of the input voltage.

3. Apply square wave or sine wave input voltage (V) or any other type of signal at the input terminal.

4. Observe the output voltage waveform on the CRO and note down the corresponding values.

5. The time constant  $R_f C_1$  is changed by changing the values of  $R_f$  or  $C_1$  and the corresponding output waveforms are noted.

6. The connection of  $R_L$  is optional.

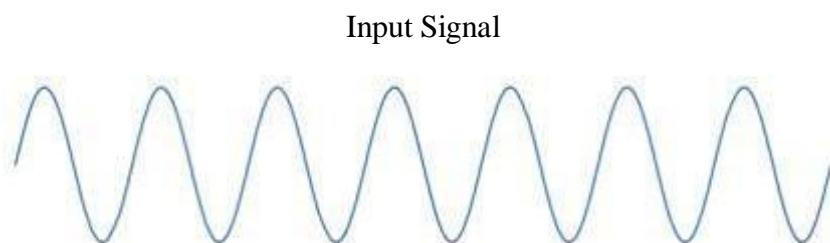

### MODEL GRAPH:

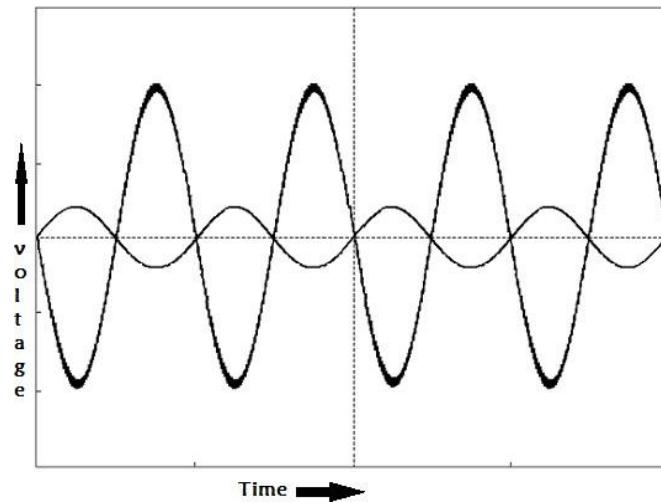

**Figure: showing the output waveforms for different input waveforms**

**THEORETICAL CALCULATIONS:**

**GRAPH SHEET:****RESULT:**

**Exercise:** List the applications of integrating amplifier and derive the expression of Integrating Amplifier

## EXPERIMENT: 11

### DIFFERENTIATOR CIRCUIT

**AIM:** To design a Differentiator Amplifier Circuit using Op-Amp.

**APPARATUS:** LM324AD/741/OP27 IC or its equivalent

100 K $\Omega$ , 1 K $\Omega$  Resistors

10nF, 100pF Capacitor

Analog Discovery Kit (AD Kit) / ESIM Software / EC Studio Software

Connecting Wires and Breadboard

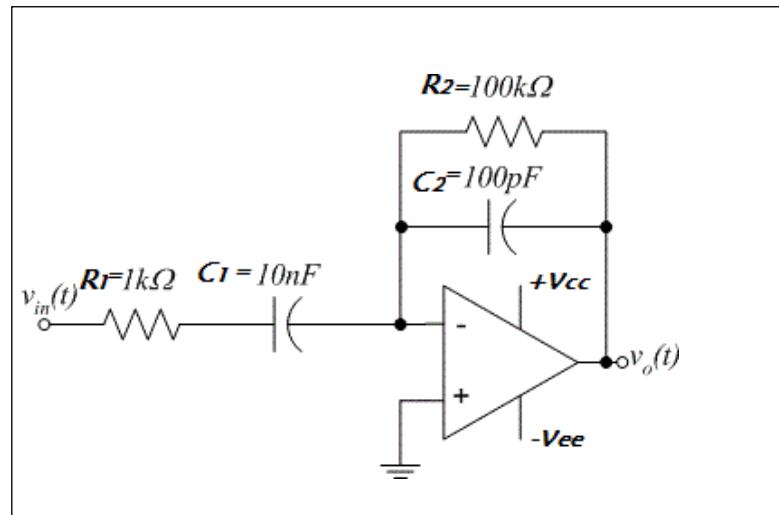

#### **CIRCUIT DIAGRAM:**

**Figure: Differentiator**

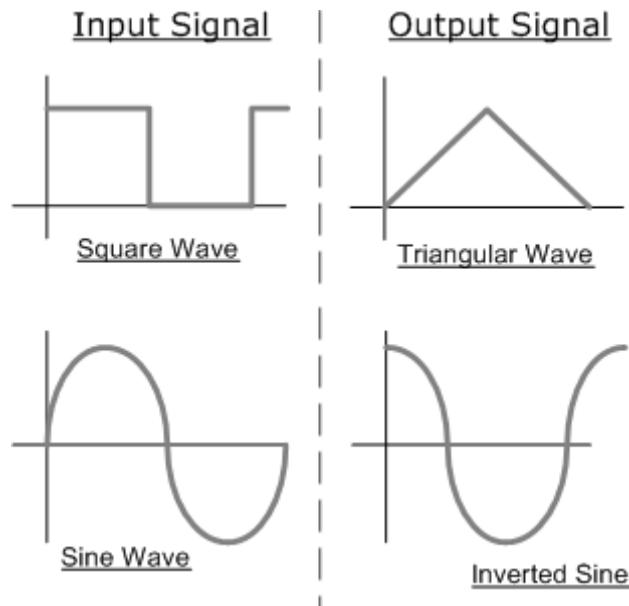

#### **THEORY:**

It consists of a high pass RC filter. It acts as a differentiator for low values of time constant. Here the output is the derivative of the input signal.

Thus, output is not only the derivative of the input but also out of phase by 180° with respect to the input.

$$V_{out} = -RC \frac{dV_{in}}{dt}$$

Here  $R_2=R$

and  $C_1=C$

## PROCEDURE:

1. Connect the circuit as shown in the circuit diagram.

2. Suitable values of  $R_1$ ,  $R_2$ ,  $C_1$ ,  $C_2$  are chosen such that the output of the circuit is the integral of the input voltage.

3. A square wave input voltage (V) is applied at the input terminal.

4. Observe the output voltage waveform on the CRO and note down the corresponding values.

5. The time constant  $R_2C_1$  is changed by changing the values of  $R_2$  or  $C_1$  and the corresponding output waveforms are noted.

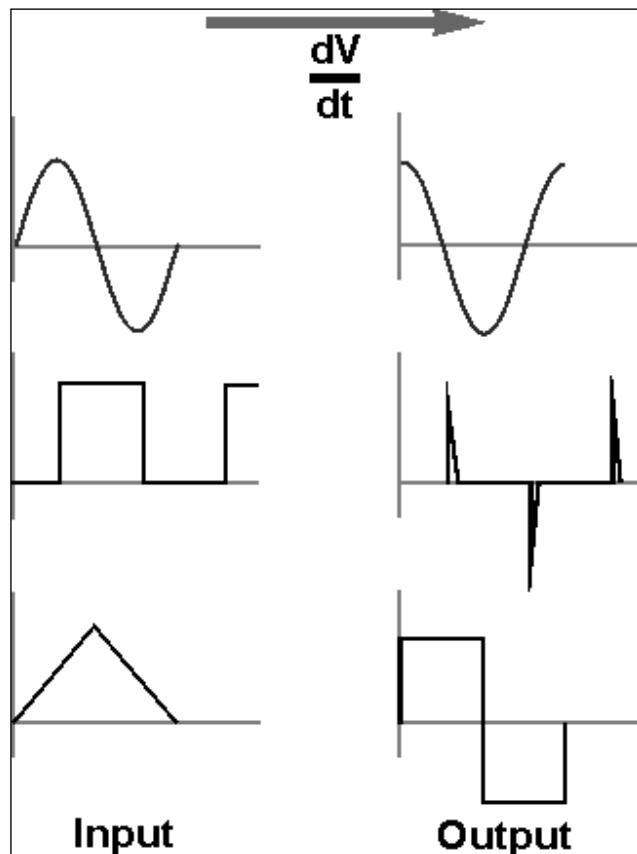

## MODEL GRAPHS:

Figure: Model output waveforms for different input signals

**THEORETICAL CALCULATIONS:**

**GRAPH SHEET:**

**RESULT:**

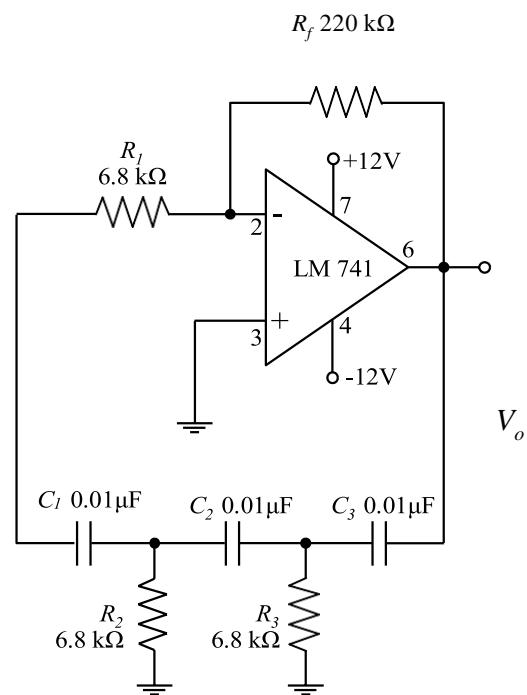

## EXPERIMENT: 12

# RC PHASE SHIFT OSCILLATOR CIRCUIT

**AIM:** To design an RC Phase Shift oscillator using op-amp for a given frequency of 1kHz.

**APPARATUS:** LM324AD/741

OP27 IC or

equivalent

10 K $\Omega$ ,

1K $\Omega$  Resistor

100nF Capacitor

Analog Discovery Kit (AD Kit) / ESIM Software /

EC Studio Software Breadboard

### THEORY

An oscillator is a circuit that produces a periodic waveform on its output with only the dc supply voltage as a required input. A repetitive input signal is not required but is sometimes used to synchronize oscillations. The output voltage can be either sinusoidal or non-sinusoidal, depending on the type of oscillator. Two major classifications for oscillators are feedback oscillator and relaxation oscillators.

Conditions for oscillation

1. The phase shift around the feedback loop must be effectively zero degrees.

2. The voltage gain,  $A_{CL}$  around the feedback loop (loop gain) must equal to (or greater than) one.

The voltage gain around the closed feedback loop,  $A_{CL}$ , is the product of the amplifier gain,  $A_v$ , and the attenuation,  $B$  of the feedback circuit.

$$A_{CL}=A_v B$$

RC phase-shift oscillator is a linear electronic oscillator circuit that produces a sine wave output. It consists of an inverting amplifier element such as a transistor or op-amp with its output fed back to its input through a phase-shift network consisting of resistors and capacitors in a ladder network. Each of the three RC networks in the

feedback loop can provide a maximum phase shift approaching 90 degrees. Oscillation occurs at the frequency where the total phase shift through the three RC network is 180 degrees. Inversion output at the output of op-amp itself produces the additional 180 degree to meet the requirement for oscillation of 360 degrees (or zero degree) phase shift around the feedback loop.

## DESIGN

The attenuation B of the three section RC feedback network is  $B = 1 / 29$

To meet the greater than unity loop gain requirement, the closed loop voltage gain of op-amp must be greater than 29.

Given frequency,  $f = 1 \text{ kHz}$ . We have  $f = \frac{1}{2\pi RC\sqrt{6}}$

Let  $R_1 = R_2 = R_3 = R$  and  $C_1 = C_2 = C_3 = C$

Select nearest value of  $220\text{ k}\Omega$  for  $R_f$

Assume  $C = 0.01\mu\text{F}$ .

$$R = \frac{1}{2\pi f C\sqrt{6}}$$

$$= \frac{1}{2\pi \times 10^3 \times 0.01 \times 10^{-6} \sqrt{6}} \\ = 6.5\text{ k}\Omega$$

Select nearest value of  $6.8\text{ k}\Omega$  for  $R$

$$R_f = A_{CL} R_i = 29 \times 6.8 \times 10^3 = 197.2\text{ k}\Omega$$